Voici une liste des projets intégrateurs proposés par l’équipe pédagogique de la filière « Système embarqué » pour les élèves en apprentissage en deuxième année lors de l’année scolaire 2023-2024.

- Capteur alimenté par récupération d’énergie

- Développement d’un espion matériel

- Mise en œuvre d’un environnement pour l’utilisation des interfaces Jtag des cartes Altera/Intel

- Sujets liés au cours de 3A 5SE02

Capteur alimenté par récupération d’énergie

Contexte

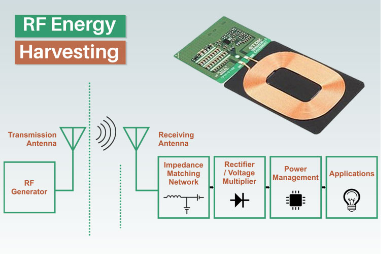

Avec la tension actuelle sur le marché des piles, il est primordial de prolonger la durée de vie des piles voire concevoir des systèmes sans pile. Pour réaliser cet objectif, on fait de plus en plus recours à la récupération d’énergie. En interne, la technique la plus répandue est la récupération d’énergie RF.

Objectif du projet

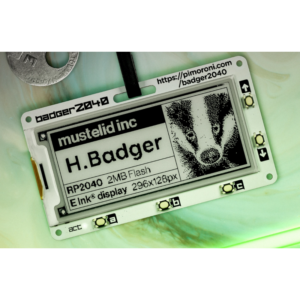

L’objectif de cet projet est de réaliser un système de récupération d’énergie et de l’intégrer avec un capteur qui s’adaptera en fonction de l’énergie récupérée. Le système envisagé est un capteur de température avec un écran e-ink dont la valeur se remettra à jour dès que le système récupération « a récolté » assez d’énergie pour réaliser cette opération. Le système de récupération, le capteur et l’écran seront intégré dans un circuit imprimé.seront intégré dans un circuit imprimé.

Description des taches

- Etat de l’art sur les systèmes de récupération RF

- Choix des composants pour le système de récupération en se basant sur des simulations et les datasheets

- Programmation du capteur pour intégrer l’aspect adaptatif

- Intégration du système sur PCB

- Faire les tests avec des mesures filaires et sans fil.

Encadrants : Chadi Jabbour et Reda Mohellebi

Nombre d’élèves : 1 ou 2

Développement d’un espion matériel

Une méthode pour attaquer un système informatique (qu’il soit embarqué ou non) est d’espionner, voire de modifier, le contenu de la mémoire vive.

Il est ainsi possible de récupérer le code et les données des applications qui s’exécutent sur le système, ou de les perturber.

Ces attaques sont possibles de plusieurs manières : en se branchant physiquement sur le bus qui relie le processeur et la mémoire, en enlevant la mémoire pour la lire (cold-boot attack), en utilisant le DMA…

Nous nous intéressons ici à la technique du man-in-the-middle sur le bus entre le processeur et la mémoire.

Le but du projet est de réaliser un démonstrateur d’un dispositif d’interception, et de modification à la volée, des informations échangées entre le processeur et la mémoire.

Pour des raisons pratiques évidente, nous implémenterons tout le système sur un FPGA (aussi bien le processeur, la mémoire, le bus et le dispositif d’espionnage).

Le projet est découpé en plusieurs étapes :

- Mise en place d’un processeur simple et de sa RAM sur un FPGA

- Développement d’un premier module transparent à positionner entre le processeur et la RAM

- Amélioration du module pour enregistrer les échanges pertinents

- Amélioration du module pour modifier des échanges quand certaines conditions sont remplies

Encadrant : Guillaume Duc

Nombre d’élèves : 1 ou 2

Mise en œuvre d’un environnement pour l’utilisation des interfaces Jtag des cartes Altera/Intel

Les cartes de références, ainsi que les cartes destinées à l’enseignement, pour les FPGA Intel/Altera, contiennent un module nommé USB-Blaster pour, entre autres, programmer les FPGA.

Ce module, permet de se connecter à un PC par une interface USB et de contrôler l’interface Jtag des FPGA.

Après la programmation du FPGA, l’interface Jtag reste disponible et pourrait être utilisée pour permettre d’autres fonctionnalités. Par exemple:

- implémenter une interface de dbug pour un processeur,

- transporter des flux de donnée arbitraires (des trames série par exemple).

Ces fonctionnalités sont déjà proposées par Intel/Altera et lié à certains de leurs outils.

Objectif du projet

Analyser le fonctionnement de cette interface et développer un environnement permettant d’utiliser cette interface en dehors des outils du fabricant.

Plus précisément:

- permettre d’accéder à l’interface de debug d’un processeur implémenté dans le FPGA (le Hazard3 par exemple),

- développer une pseudo UART connectée à ce processeur et transportant les trames série,

- identifier et mettre en œuvre les outils logiciels permettant de contrôler cette interface pour les deux usages.

L’environnement développé se divise en deux:

- un ensemble de primitives (modules) matériels (en SystemVerilog),

- un ensemble d’outils logiciels pour la configuration et l’accès à partir d’un PC Linux.

Références

- https://en.wikipedia.org/wiki/JTAG

- https://www.intel.com/content/www/us/en/docs/programmable/683705/20-3/introduction.html

- https://openocd.org/doc-release/doxygen/usb__blaster_8c_source.html

- https://github.com/binary-logic/vj-uart

- https://tomverbeure.github.io/2021/10/30/Intel-JTAG-Primitive.html

- https://github.com/pgate1/USB-Blaster_UART

- https://ixo-jtag.sourceforge.net/

- https://github.com/Wren6991/Hazard3

Encadrant : Tarik Graba

Élèves : 1 ou 2

Sujets liés au cours de 3A 5SE02

Trois sujets liés au cours de 3A 5SE02 peuvent être choisis :

- Defining nudging strategies in the specification of properties for multi-agent systems

- Towards the verification of smart contracts

- Defining dynamic coalitions within the specification of properties for multi-agent systems

Encadrant : Vadim Malvone

Élèves : voir sujets